HYB18T256400AF(L) HYB18T256800AF(L) HYB18T256160AF(L)

256-Mbit DDR2 SDRAM

DDR2 SDRAM

RoHS Compliant Products

Qimonda

| HYB18T25                             | HYB18T256400AF(L), HYB18T256800AF(L), HYB18T256160AF(L)                    |  |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|

| Revision History: 2007-01, Rev. 1.41 |                                                                            |  |  |  |  |  |  |

| Page                                 | Page Subjects (major changes since last revision)                          |  |  |  |  |  |  |

| All                                  | Qimonda update                                                             |  |  |  |  |  |  |

| All                                  | Adapted internet edition                                                   |  |  |  |  |  |  |

| Previous F                           | Revision: 2005-07, Rev. 1.4                                                |  |  |  |  |  |  |

|                                      | Added low-power components HYB18T256[40/80/16]0AFL-3.7                     |  |  |  |  |  |  |

|                                      | Added DDR2-800 5-5-5 components                                            |  |  |  |  |  |  |

| 92                                   | Updated $I_{\rm DD}$ Currents ( $I_{\rm DD2P},I_{\rm DD3P1},I_{\rm DD6}$ ) |  |  |  |  |  |  |

| Chapter 2                            | Updated Pin Configuration - various editorial changes on notes             |  |  |  |  |  |  |

| Previous F                           | Previous Revision: 2005-07, Rev. 1.3                                       |  |  |  |  |  |  |

#### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

techdoc@qimonda.com

# 1 Overview

This chapter gives an overview of the 256-Mbit DDR2 SDRAM product family and describes its main characteristics.

## 1.1 Features

The 256-Mbit DDR2 SDRAM offers the following key features:

- 1.8 V ± 0.1 V Power Supply 1.8 V ± 0.1 V (SSTL\_18) compatible I/O

- DRAM organisations with 4, 8 data in/outputs

- Double Data Rate architecture: two data transfers per clock cycle, four internal banks for concurrent operation

- CAS Latency: 3, 4

- · Burst Length: 4 and 8

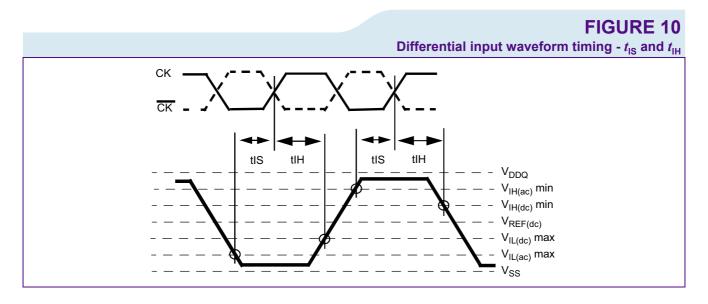

- Differential clock inputs (CK and CK)

- Bi-directional, differential data strobes (DQS and DQS) are transmitted / received with data. Edge aligned with read data and center-aligned with write data.

- · DLL aligns DQ and DQS transitions with clock

- DQS can be disabled for single-ended data strobe operation

- Commands entered on each positive clock edge, data and data mask are referenced to both edges of DQS

- · Data masks (DM) for write data

- Posted CAS by programmable additive latency for better command and data bus efficiency

- Off-Chip-Driver impedance adjustment (OCD) and On-Die-Termination (ODT) for better signal quality.

- · Auto-Precharge operation for read and write bursts

- Auto-Refresh, Self-Refresh and power saving Power-Down modes

- Average Refresh Period 7.8  $\mu s$  at a  $T_{\rm CASE}$  lower than 85 °C, 3.9  $\mu s$  between 85 °C and 95 °C

- · High Temperature Self Refresh Mode is supported

- · Full and reduced Strength Data-Output Drivers

- · 1KByte page size

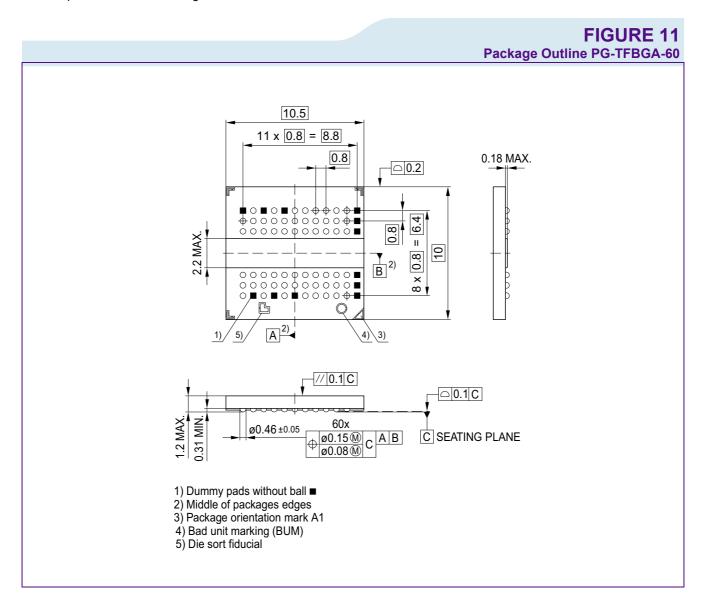

- · Lead-free Packages: P-TFBGA-60

- RoHS Compliant Products<sup>1)</sup>

# TABLE 1 Performance tables for -2 5(F)

|                                  |        |               |                 | Performance tables for - | ·2.5(F) |

|----------------------------------|--------|---------------|-----------------|--------------------------|---------|

| Product Type Speed Co            | ode    |               | -2.5F           | -2.5                     | Unit    |

| Speed Grade                      |        |               | DDR2-800D 5-5-5 | DDR2-800E 6-6-6          | _       |

| Max. Clock Frequency             | @CL6   | $f_{\rm CK6}$ | 400             | 400                      | MHz     |

|                                  | @CL5   | $f_{ m CK5}$  | 400             | 333                      | MHz     |

|                                  | @CL4 f |               | 266             | 266                      | MHz     |

|                                  | @CL3   | $f_{CK3}$     | 200             | 200                      | MHz     |

| Min. RAS-CAS-Delay $t_{RCD}$     |        |               | 12.5            | 15                       | ns      |

| Min. Row Precharge Time $t_{RP}$ |        |               | 12.5            | 15                       | ns      |

| Min. Row Active Time $t_{RAS}$   |        |               | 45              | 45                       | ns      |

| Min. Row Cycle Time              |        | $t_{RC}$      | 57.5            | 60                       | ns      |

<sup>1)</sup> RoHS Compliant Product: Restriction of the use of certain hazardous substances (RoHS) in electrical and electronic equipment as defined in the directive 2002/95/EC issued by the European Parliament and of the Council of 27 January 2003. These substances include mercury, lead, cadmium, hexavalent chromium, polybrominated biphenyls and polybrominated biphenyl ethers.

|          | _ | _  |

|----------|---|----|

| <br>_    | _ | -, |

|          |   | _  |

| <b>.</b> |   |    |

| i citotilianoc tabic for | 0(0)    |

|--------------------------|---------|

| s                        | Unit    |

| DR2-667D 5-5-5           | _       |

| 3                        | MHz     |

| 0                        | N 41 1- |

Performance table for -3(S)

| Product Type Speed Code Speed Grade |      |           | -3              | <b>-3</b> S     | Unit |

|-------------------------------------|------|-----------|-----------------|-----------------|------|

|                                     |      |           | DDR2-667C 4-4-4 | DDR2-667D 5-5-5 | _    |

| Max. Clock Frequency @CL5           |      | $f_{CK5}$ | 333             | 333             | MHz  |

|                                     | @CL4 | $f_{CK4}$ | 333             | 266             | MHz  |

|                                     | @CL3 | $f_{CK3}$ | 200             | 200             | MHz  |

| Min. RAS-CAS-Delay $t_{RCD}$        |      |           | 12              | 15              | ns   |

| Min. Row Precharge Time $t_{RP}$    |      |           | 12              | 15              | ns   |

| Min. Row Active Time $t_{RAS}$      |      |           | 45              | 45              | ns   |

| Min. Row Cycle Time                 |      | $t_{RC}$  | 57              | 60              | ns   |

|                                  |                                  |               | High Performance | ce for DDR2-400B and L | JDK2-533C |

|----------------------------------|----------------------------------|---------------|------------------|------------------------|-----------|

| Product Type Speed Code          |                                  |               | -3.7             | <b>-</b> 5             | Unit      |

| Speed Grade                      |                                  |               | DDR2-533C 4-4-4  | DDR2-400B 3-3-3        | _         |

| max. Clock Frequency             | @CL5                             | $f_{\rm CK5}$ | 266              | 200                    | MHz       |

|                                  | @CL4                             | $f_{\rm CK4}$ | 266              | 200                    | MHz       |

|                                  | @CL3                             | $f_{CK3}$     | 200              | 200                    | MHz       |

| min. RAS-CAS-Delay               | min. RAS-CAS-Delay $t_{\sf RCD}$ |               |                  | 15                     | ns        |

| min. Row Precharge Time $t_{RP}$ |                                  |               | 15               | 15                     | ns        |

| min. Row Active Time $t_{RAS}$   |                                  |               | 45               | 40                     | ns        |

| min. Row Cycle Time $t_{\rm RC}$ |                                  |               | 60               | 55                     | ns        |

#### 1.2 Description

The 256-Mbit DDR2 DRAM is a high-speed Double-Data-Rate-Two **CMOS** Synchronous DRAM device containing268,435,456 bits and internally configured as a quad-bank DRAM. The 256-Mbit device is organized as either 16 Mbit  $\times$  4 I/O  $\times$  4 banks, 8 Mbit  $\times$  8 I/O  $\times$  4 banks or 4 Mbit  $\times$  16 I/O  $\times$  4 banks chip. These synchronous devices achieve high speed transfer rates starting at 400 Mbit/sec/pin for general applications. See Table 1, Table 2 and Table 3 for performance figures.

The device is designed to comply with all DDR2 DRAM key features.

- 1. posted CAS with additive latency,

- 2. write latency = read latency 1,

- 3. normal and weak strength data-output driver,

- 4. Off-Chip Driver (OCD) impedance adjustment

#### 5. On-Die Termination (ODT) function.

All of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the cross point of differential clocks (CK rising and CK falling). All I/Os are synchronized with a single ended DQS or differential DQS-DQS pair in a source synchronous fashion.

A 15 bit address bus is used to convey row, column and bank address information.

The DDR2 device operates with a 1.8 V  $\pm$  0.1 V power supply. An Auto-Refresh and Self-Refresh mode is provided along with various power-saving power-down modes.

The DDR2 SDRAM is available in P-TFBGA package.

# 1.3 Ordering Information

This chapter contains the ordering information.

|                     |      |          |                                                                   |                |                                                                   |                | <b>TABLE 4</b> |

|---------------------|------|----------|-------------------------------------------------------------------|----------------|-------------------------------------------------------------------|----------------|----------------|

|                     |      |          | Orde                                                              | ering Info     | ormation for RoHS                                                 | S compli       | ant products   |

| Part Number         | Org. | Speed    | CAS <sup>1)</sup> RCD <sup>2)</sup> RP <sup>3)</sup><br>Latencies | Clock<br>(MHz) | CAS <sup>1)</sup> RCD <sup>2)</sup> RP <sup>3)</sup><br>Latencies | Clock<br>(MHz) | Package        |

| HYB18T256400AF-2.5  | ×4   | DDR2-800 | 6–6–6                                                             | 400            | 5–5–5                                                             | 333            | P-TFBGA-60     |

| HYB18T256800AF-2.5  | ×8   |          |                                                                   |                |                                                                   |                |                |

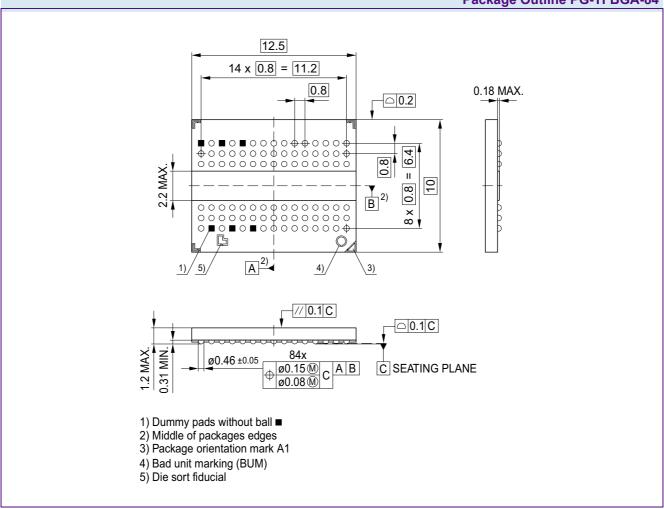

| HYB18T256160AF-2.5  | ×16  |          |                                                                   |                |                                                                   |                | P-TFBGA-84     |

| HYB18T256400AF-25F  | ×4   |          | 5–5–5                                                             | 400            | 4-4-4                                                             | 333            | P-TFBGA-60     |

| HYB18T256800AF-25F  | ×8   |          |                                                                   |                |                                                                   |                |                |

| HYB18T256160AF-25F  | ×16  |          |                                                                   |                |                                                                   |                | P-TFBGA-84     |

| HYB18T256400AF-3    | ×4   | DDR2-667 | 4-4-4                                                             | 333            | 3–3–3                                                             | 200            | P-TFBGA-60     |

| HYB18T256800AF-3    | ×8   |          |                                                                   |                |                                                                   |                |                |

| HYB18T256160AF-3    | ×16  |          |                                                                   |                |                                                                   |                | P-TFBGA-84     |

| HYB18T256400AF-3S   | ×4   |          | 5–5–5                                                             | 333            | 4-4-4                                                             | 266            | P-TFBGA-60     |

| HYB18T256800AF-3S   | ×8   |          |                                                                   |                |                                                                   |                |                |

| HYB18T256160AF-3S   | ×16  |          |                                                                   |                |                                                                   |                | P-TFBGA-84     |

| HYB18T256400AF-3.7  | ×4   | DDR2-533 | 4-4-4                                                             | 266            | 3–3–3                                                             | 200            | P-TFBGA-60     |

| HYB18T256800AF-3.7  | ×8   |          |                                                                   |                |                                                                   |                |                |

| HYB18T256160AF-3.7  | ×16  |          |                                                                   |                |                                                                   |                | P-TFBGA-84     |

| HYB18T256400AFL-3.7 | ×4   |          | 4-4-4                                                             | 266            | 3–3–3                                                             | 200            | P-TFBGA-60     |

| HYB18T256800AFL-3.7 | ×8   |          |                                                                   |                |                                                                   |                |                |

| HYB18T256160AFL-3.7 | ×16  |          |                                                                   |                |                                                                   |                | P-TFBGA-84     |

| HYB18T256400AF-5    | ×4   | DDR2-400 | 3–3–3                                                             | 200            | _                                                                 |                | P-TFBGA-60     |

| HYB18T256800AF-5    | ×8   |          |                                                                   |                |                                                                   |                |                |

| HYB18T256160AF-5    | ×16  |          |                                                                   |                |                                                                   |                | P-TFBGA-84     |

<sup>1)</sup> CAS: Column Adress Strobe

Note: For product nomenclature see Chapter 9 of this data sheet

<sup>2)</sup> RCD: Row Column Delay

<sup>3)</sup> RP: Row Precharge

# 2 Pin Configuration

The pin configuration of a DDR2 SDRAM is listed by function in **Table 5**. The abbreviations used in the Pin# and Buffer Type columns are explained in **Table 6** and **Table 7** respectively. The pin numbering for the FBGA package is depicted in **Figure 1** for  $\times$ 4, **Figure 2** for  $\times$ 8 and **Figure 3** for  $\times$ 16.

|            |                 |             |                | TABLE 5                                                      |

|------------|-----------------|-------------|----------------|--------------------------------------------------------------|

|            |                 |             |                | Pin Configuration of DDR2 SDRAM                              |

| Pin#       | Name            | Pin<br>Type | Buffer<br>Type | Function                                                     |

| Clock Sign | nals ×4/×8 Orga | anization   |                |                                                              |

| E8         | CK              | I           | SSTL           | Clock Signal CK, Complementary Clock Signal CK               |

| F8         | CK              | I           | SSTL           |                                                              |

| F2         | CKE             | I           | SSTL           | Clock Enable                                                 |

| Clock Sigr | nals ×16 Organ  | ization     |                |                                                              |

| J8         | CK              | I           | SSTL           | Clock Signal CK, Complementary Clock Signal CK               |

| K8         | CK              | I           | SSTL           | Note: See functional description in x4/x8 organization       |

| K2         | CKE             | I           | SSTL           | Clock Enable                                                 |

|            |                 |             |                | Note: See functional description in x4/x8 organization       |

| Control Si | gnals ×4/×8 Or  | ganizatio   | ns             |                                                              |

| F7         | RAS             | I           | SSTL           | Row Address Strobe (RAS), Column Address Strobe (CAS), Write |

| G7         | CAS             | I           | SSTL           | Enable (WE)                                                  |

| F3         | WE              | I           | SSTL           |                                                              |

| G8         | CS              | I           | SSTL           | Chip Select                                                  |

| Control Si | gnals ×16 Orga  | anization   |                |                                                              |

| K7         | RAS             | I           | SSTL           | Row Address Strobe (RAS), Column Address Strobe (CAS), Write |

| L7         | CAS             | I           | SSTL           | Enable (WE)                                                  |

| K3         | WE              | I           | SSTL           |                                                              |

| L8         | CS              | I           | SSTL           | Chip Select                                                  |

| Address S  | ignals ×4/×8 O  | rganizatio  | ons            | •                                                            |

| G2         | BA0             | I           | SSTL           | Bank Address Bus 1:0                                         |

| G3         | BA1             | I           | SSTL           |                                                              |

|            |                 |             |                |                                                              |

| Pin#         | Name          | Pin<br>Type | Buffer<br>Type | Function                                             |

|--------------|---------------|-------------|----------------|------------------------------------------------------|

| H8           | A0            | I           | SSTL           | Address Signal 12:0, Address Signal 10/Autoprecharge |

| H3           | A1            | ı           | SSTL           |                                                      |

| H7           | A2            | I           | SSTL           |                                                      |

| J2           | A3            | I           | SSTL           |                                                      |

| J8           | A4            | I           | SSTL           |                                                      |

| J3           | A5            | I           | SSTL           |                                                      |

| J7           | A6            | I           | SSTL           |                                                      |

| K2           | A7            | I           | SSTL           |                                                      |

| K8           | A8            | I           | SSTL           |                                                      |

| K3           | A9            | I           | SSTL           |                                                      |

| H2           | A10           | I           | SSTL           |                                                      |

|              | AP            | I           | SSTL           |                                                      |

| K7           | A11           | ı           | SSTL           |                                                      |

| L2           | A12           | I.          | SSTL           |                                                      |

| L8           | A13           | I           | SSTL           | Address Signal 13                                    |

|              |               |             |                | Note: 256 Mbit components                            |

|              | NC            | _           | _              |                                                      |

| Address Sig  | ınals ×16 Org | anization   |                |                                                      |

| L2           | BA0           | I           | SSTL           | Bank Address Bus 1:0                                 |

| L3           | BA1           | I           | SSTL           |                                                      |

| L1           | NC            | _           | _              |                                                      |

| M8           | A0            | I           | SSTL           | Address Signal 12:0, Address Signal 10/Autoprecharge |

| M3           | A1            | I           | SSTL           |                                                      |

| M7           | A2            | I           | SSTL           |                                                      |

| N2           | A3            | I           | SSTL           |                                                      |

| N8           | A4            | I           | SSTL           |                                                      |

| N3           | A5            | I           | SSTL           |                                                      |

| N7           | A6            | I           | SSTL           |                                                      |

| P2           | A7            | I           | SSTL           |                                                      |

| P8           | A8            | I           | SSTL           |                                                      |

| P3           | A9            | I           | SSTL           |                                                      |

| M2           | A10           | I           | SSTL           |                                                      |

|              | AP            | I           | SSTL           |                                                      |

| P7           | A11           | I           | SSTL           |                                                      |

| R2           | A12           | I           | SSTL           |                                                      |

| Data Signals | s ×4/×8 Orgai | nizations   |                |                                                      |

| C8           | DQ0           | I/O         | SSTL           | Data Signal 3:0                                      |

| C2           | DQ1           | I/O         | SSTL           |                                                      |

| D7           | DQ2           | I/O         | SSTL           |                                                      |

| D3           | DQ3           | I/O         | SSTL           |                                                      |

| Pin#            | Name             | Pin<br>Type | Buffer<br>Type | Function               |

|-----------------|------------------|-------------|----------------|------------------------|

| Data Signals ×8 | ⊔<br>8 Organizat | ion         |                |                        |

| C8              | DQ0              | I/O         | SSTL           | Data Signal 7:0        |

| C2              | DQ1              | I/O         | SSTL           |                        |

| D7              | DQ2              | I/O         | SSTL           |                        |

| D3              | DQ3              | I/O         | SSTL           |                        |

| D1              | DQ4              | I/O         | SSTL           |                        |

| D9              | DQ5              | I/O         | SSTL           |                        |

| B1              | DQ6              | I/O         | SSTL           |                        |

| B9              | DQ7              | I/O         | SSTL           |                        |

| Data Signals ×1 | 6 Organiza       | ition       | '              |                        |

| G8              | DQ0              | I/O         | SSTL           | Data Signal 15:0       |

| G2              | DQ1              | I/O         | SSTL           |                        |

| H7              | DQ2              | I/O         | SSTL           |                        |

| H3              | DQ3              | I/O         | SSTL           |                        |

| H1              | DQ4              | I/O         | SSTL           |                        |

| H9              | DQ5              | I/O         | SSTL           |                        |

| F1              | DQ6              | I/O         | SSTL           |                        |

| F9              | DQ7              | I/O         | SSTL           |                        |

| C8              | DQ8              | I/O         | SSTL           |                        |

| C2              | DQ9              | I/O         | SSTL           |                        |

| D7              | DQ10             | I/O         | SSTL           |                        |

| D3              | DQ11             | I/O         | SSTL           |                        |

| D1              | DQ12             | I/O         | SSTL           |                        |

| D9              | DQ13             | I/O         | SSTL           |                        |

| B1              | DQ14             | I/O         | SSTL           |                        |

| B9              | DQ15             | I/O         | SSTL           |                        |

| Data Strobe ×4/ | ×8 organis       | ations      |                |                        |

| B7              | DQS              | I/O         | SSTL           | Data Strobe            |

| A8              | DQS              | I/O         | SSTL           |                        |

| B3              | RDQS             | 0           | SSTL           | Read Data Strobe       |

| A2              | RDQS             | 0           | SSTL           |                        |

| Data Strobe ×10 | 6 Organizat      | tion        |                |                        |

| B7              | UDQS             | I/O         | SSTL           | Data Strobe Upper Byte |

| A8              | UDQS             | I/O         | SSTL           |                        |

| F7              | LDQS             | I/O         | SSTL           | Data Strobe Lower Byte |

| E8              | LDQS             | I/O         | SSTL           |                        |

| Data Mask ×4/×  | 8 Organiza       | tions       |                |                        |

| B3              | DM               | I           | SSTL           | Data Mask              |

| Pin#                                   | Name                | Pin<br>Type | Buffer<br>Type | Function                   |

|----------------------------------------|---------------------|-------------|----------------|----------------------------|

| Data Mask ×16                          | Organizatio         | n           | 1              |                            |

| B3                                     | UDM                 | I           | SSTL           | Data Mask Upper/Lower Byte |

| F3                                     | LDM                 | I           | SSTL           |                            |

| Power Supplies                         | ×4/×8/×16           | Organiza    | tions          |                            |

| A9,C1,C3,C7,<br>C9                     | $V_{DDQ}$           | PWR         | _              | I/O Driver Power Supply    |

| A1                                     | $V_{DD}$            | PWR         | _              | Power Supply               |

| A7,B2,B8,D2,<br>D8                     | $V_{\rm SSQ}$       | PWR         | _              | I/O Driver Power Supply    |

| A3,E3                                  | $V_{\rm SS}$        | PWR         | _              | Power Supply               |

| Power Supplies                         | ×4/×8 Orga          | anizations  | S              |                            |

| E2                                     | $V_{REF}$           | Al          | _              | I/O Reference Voltage      |

| E1                                     | $V_{DDL}$           | PWR         | _              | Power Supply               |

| E9,H9,L1                               | $V_{DD}$            | PWR         | _              | Power Supply               |

| E7                                     | $V_{\mathrm{SSDL}}$ | PWR         | _              | Power Supply               |

| J1,K9                                  | $V_{\rm SS}$        | PWR         | _              | Power Supply               |

| Power Supplies                         | ×16 Organ           | ization     |                |                            |

| J2                                     | $V_{REF}$           | Al          | _              | I/O Reference Voltage      |

| E9, G1, G3, G7,<br>G9                  | $V_{DDQ}$           | PWR         | _              | I/O Driver Power Supply    |

| J1                                     | $V_{DDL}$           | PWR         | _              | Power Supply               |

| E1, J9, M9, R1                         | $V_{DD}$            | PWR         | _              | Power Supply               |

| E7, F2, F8, H2,<br>H8                  | $V_{SSQ}$           | PWR         | _              | I/O Driver Power Supply    |

| J7                                     | $V_{SSDL}$          | PWR         | _              | Power Supply               |

| A3,<br>E3,J3,N1,P9                     | $V_{\rm SS}$        | PWR         | _              | Power Supply               |

| Not Connected                          | ×4/×8 Orga          | nizations   |                |                            |

| A2, B1, B9, D1,<br>D9,G1, L3,L7,<br>L8 | NC                  | NC          | _              | Not Connected              |

| Not Connected                          | ×16 Organi          | zation      |                |                            |

| A2, E2, L1, R3,<br>R7, R8              | NC                  | NC          | _              | Not Connected              |

| Other Pins ×4/×                        | 8 Organiza          | tions       |                |                            |

| F9                                     | ODT                 | I           | SSTL           | On-Die Termination Control |

| Other Pins ×16                         | Organizatio         | on          |                |                            |

| K9                                     | ODT                 | I           | SSTL           | On-Die Termination Control |

### **TABLE 6**

#### **Abbreviations for Pin Type**

|              | Abbieviations for i'm Type                  |

|--------------|---------------------------------------------|

| Abbreviation | Description                                 |

| 1            | Standard input-only pin. Digital levels.    |

| 0            | Output. Digital levels.                     |

| I/O          | I/O is a bidirectional input/output signal. |

| Al           | Input. Analog levels.                       |

| PWR          | Power                                       |

| GND          | Ground                                      |

| NC           | Not Connected                               |

## **TABLE 7**

#### Abbreviations for Buffer Type

|              | Appreviations for Buffer Type                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Abbreviation | Description                                                                                                                             |

| SSTL         | Serial Stub Terminated Logic (SSTL_18)                                                                                                  |

| LV-CMOS      | Low Voltage CMOS                                                                                                                        |

| CMOS         | CMOS Levels                                                                                                                             |

| OD           | Open Drain. The corresponding pin has 2 operational states, active low and tristate, and allows multiple devices to share as a wire-OR. |

# 2.1 TFBGA Ball Out Diagrams

This chapter contains the TFBGA Ball Out Diagrams.

|    |              |               | P            | in Con   | figurati | ion foi | r v4 co           | mnone     | nte P                                  | FIGURE 1 G-TFBGA-60 (top view) |

|----|--------------|---------------|--------------|----------|----------|---------|-------------------|-----------|----------------------------------------|--------------------------------|

|    |              |               |              | 111 0011 | iigurati |         | \ <del>-</del>    | пропе     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | C-11 BOA-00 (top view)         |

|    | 1            | 2             | 3            | 4        | 5        | 6       | 7                 | 8         | 9                                      |                                |

|    | $V_{DD}$     | NC            | $V_{SS}$     |          | Α        |         | $V_{SSQ}$         | DQS       | $V_{DDQ}$                              |                                |

|    | NC           | $V_{SSQ}$     | DM           |          | В        |         | DQS               | $V_{SSQ}$ | NC                                     |                                |

|    | $V_{DDQ}$    | DQ1           | $V_{DDQ}$    |          | С        |         | $V_{DDQ}$         | DQ0       | $V_{DDQ}$                              |                                |

|    | NC           | $V_{\rm SSQ}$ | DQ3          |          | D        |         | DQ2               | $V_{SSQ}$ | NC                                     |                                |

|    | $V_{DDL}$    | $V_{REF}$     | $V_{\rm SS}$ |          | Е        |         | V <sub>SSDL</sub> | СК        | $V_{DD}$                               |                                |

|    |              | CKE           | WE           |          | F        |         | RAS               | <u>ск</u> | ODT                                    |                                |

| [1 | NC, BA2      | BA0           | BA1          |          | G        |         | CAS               | <br>cs    |                                        | •                              |

|    |              | A10/AP        | A1           |          | Н        |         | A2                | A0        | $V_{DD}$                               |                                |

|    | $V_{\rm SS}$ | А3            | A5           |          | J        |         | A6                | A4        |                                        | •                              |

|    |              | A7            | A9           |          | K        |         | A11               | A8        | $V_{\rm SS}$                           |                                |

|    | $V_{DD}$     | A12           | NC           |          | L        |         | NC                | NC, A13   |                                        | •                              |

|    | •            |               |              |          |          |         |                   |           | MPPT0020                               | 0                              |

- 1.  $V_{\rm DDL}$  and  $V_{\rm SSDL}$  are power and ground for the DLL.  $V_{\rm DDL}$  is connected to  $V_{\rm DD}$  on the device.  $V_{\rm DD}$ ,  $V_{\rm DDQ}$ ,  $V_{\rm SSDL}$ ,  $V_{\rm SS}$ , and  $V_{\rm SSQ}$  are isolated on the device.

- 2. Ball position L8 is A13 for 512-Mbit and is Not Connected on 256-Mbit

# FIGURE 2 Pin Configuration for ×8 components, PG-TFBGA-60-24

| 1                 | 2            | 3                  | 4 | 5 | 6 | 7                 | 8             | 9                 |   |

|-------------------|--------------|--------------------|---|---|---|-------------------|---------------|-------------------|---|

| $V_{DD}$          | NC,<br>RDQS  | $V_{\rm SS}$       |   | Α |   | $V_{ m SSQ}$      | DQS           | $V_{DDQ}$         |   |

| DQ6               | $V_{ m SSQ}$ | DM/<br>RDQS        |   | В |   | DQS               | $V_{ m SSQ}$  | DQ7               |   |

| $V_{DDG}$         | DQ1          | $V_{\mathtt{DDQ}}$ |   | С |   | $V_{DDQ}$         | DQ0           | $V_{DDQ}$         |   |

| DQ4               | $V_{ m SSQ}$ | DQ3                |   | D |   | DQ2               | $V_{\rm SSQ}$ | DQ5               |   |

| $V_{	extsf{DDL}}$ | $V_{REF}$    | $V_{\rm SS}$       |   | Е |   | V <sub>SSDL</sub> | СК            | $V_{DD}$          |   |

|                   | CKE          | WE                 |   | F |   | RAS               | СK            | ODT               |   |

| NC                | BA0          | BA1                |   | G |   | CAS               | <del>CS</del> |                   |   |

|                   | A10/AP       | A1                 |   | Н |   | A2                | A0            | $V_{DD}$          |   |

| $V_{	extsf{SS}}$  | A3           | A5                 |   | J |   | A6                | A4            |                   |   |

|                   | A7           | A9                 |   | K |   | A11               | A8            | $V_{\mathrm{SS}}$ |   |

| $V_{DD}$          | A12          | NC                 |   | L |   | NC                | NC,A13        |                   |   |

|                   |              |                    |   |   |   |                   |               | MPPT0090          | ) |

- 1. RDQS / RDQS are enabled by EMRS(1) command.

- 2. If RDQS /  $\overline{RDQS}$  is enabled, the DM function is disabled

- 3. When enabled, RDQS &  $\overline{RDQS}$  are used as strobe signals during reads.

- 4.  $V_{\rm DDL}$  and  $V_{\rm SSDL}$  are power and ground for the DLL.  $V_{\rm DDL}$  is connected to  $V_{\rm DD}$  on the device.  $V_{\rm DD}$ ,  $V_{\rm DDQ}$ ,  $V_{\rm SSDL}$ ,  $V_{\rm SS}$ , and  $V_{\rm SSQ}$  are isolated on the device.

- 5. Ball position L8 is A13 for 512-Mbit and is Not Connected on 256-Mbit.

# FIGURE 3 Pin Configuration for ×16 components. PG-TFBGA-84-8

| 1                                                                                                                                                                                                                                                                                                                               |              |               |                 |   | 1 111 00 | mgara | tion for      | ×10 00        | тропо        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|-----------------|---|----------|-------|---------------|---------------|--------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                          |              |               |                 |   |          |       |               |               |              |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | 1            | 2             | 3               | 4 | 5        | 6     | 7             | 8             | 9            |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | $V_{DD}$     | NC            | $V_{\rm SS}$    |   | Α        |       | $V_{\rm SSQ}$ | UDQS          | $V_{DDQ}$    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | DQ14         | $V_{\rm SSQ}$ | UDM             |   | В        |       | UDQS          | $V_{\rm SSQ}$ | DQ15         |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | $V_{DDQ}$    | DQ9           | $V_{DDQ}$       |   | С        |       | $V_{DDQ}$     | DQ8           | $V_{DDQ}$    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | DQ12         | $V_{\rm SSQ}$ | DQ11            |   | D        |       | DQ10          | $V_{\rm SSQ}$ | DQ13         |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | $V_{DD}$     | NC            | V <sub>SS</sub> |   | E        |       | $V_{SSQ}$     | LDQS          | $V_{DDQ}$    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | DQ6          | $V_{\rm SSQ}$ | LDM             |   | F        |       | LDQS          | $V_{\rm SSQ}$ | DQ7          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | $V_{DDQ}$    | DQ1           | $V_{DDQ}$       |   | G        |       | $V_{DDQ}$     | DQ0           | $V_{DDQ}$    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | DQ4          | $V_{\rm SSQ}$ | DQ3             |   | Н        |       | DQ2           | $V_{\rm SSQ}$ | DQ5          |

| NC         BA0         BA1         L $\overline{\text{CAS}}$ $\overline{\text{CS}}$ A10/AP         A1         M         A2         A0 $V_{DD}$ $V_{SS}$ A3         A5         N         A6         A4           A7         A9         P         A11         A8 $V_{SS}$ $V_{DD}$ A12         NC         R         NC         NC | $V_{DDL}$    | $V_{REF}$     | $V_{\rm SS}$    |   | J        |       | VSSDL         | СК            | $V_{DD}$     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                          |              | CKE           | WE              |   | K        |       | RAS           | CK            | ODT          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                           | NC           | BA0           | BA1             |   | L        |       | CAS           | cs            |              |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                          |              | A10/AP        | A1              |   | М        |       | A2            | A0            | $V_{DD}$     |

| $V_{ m DD}$ A12 NC R NC NC                                                                                                                                                                                                                                                                                                      | $V_{\rm SS}$ | А3            | A5              |   | N        |       | A6            | A4            |              |

|                                                                                                                                                                                                                                                                                                                                 |              | A7            | A9              |   | Р        |       | A11           | A8            | $V_{\rm SS}$ |

| MPPT012                                                                                                                                                                                                                                                                                                                         | $V_{DD}$     | A12           | NC              |   | R        |       | NC            | NC            |              |

|                                                                                                                                                                                                                                                                                                                                 |              |               |                 | • |          |       |               |               | MPPT012      |

- 1. UDQS/UDQS is data strobe for DQ[15:8], LDQS/LDQS is data strobe for DQ[7:0]

- LDM is the data mask signal for DQ[7:0], UDM is the data mask signal for DQ[15:8]

V<sub>DDL</sub> and V<sub>SSDL</sub> are power and ground for the DLL. V<sub>DDL</sub> is connected to V<sub>DD</sub> on the device. V<sub>DD</sub>, V<sub>DDQ</sub>, V<sub>SSDL</sub>, V<sub>SS</sub>, and V<sub>SSQ</sub> are isolated on the device.

#### 2.2 256 Mbit DDR2 Addressing

This chapter contains the 256 Mbit DDR2 Addressing.

|                               |             |           |           | ABLE 8 |

|-------------------------------|-------------|-----------|-----------|--------|

| Configuration                 | 64Mb x 4    | 32Mb x 8  | 16Mb x 16 | Note   |

| Bank Address                  | BA[1:0]     | BA[1:0]   | BA[1:0]   | _      |

| Number of Banks               | 4           | 4         | 4         | _      |

| Auto-Precharge                | A10 / AP    | A10 / AP  | A10 / AP  | _      |

| Row Address                   | A[12:0]     | A[12:0]   | A[12:0]   | _      |

| Column Address                | A11, A[9:0] | A[9:0]    | A[8:0]    | _      |

| Number of Column Address Bits | 11          | 10        | 10        | 1)     |

| Number of I/Os                | 4           | 8         | 16        | 2)     |

| Page Size [Bytes]             | 1024 (1K)   | 1024 (1K) | 1024 (1K) | 3)     |

<sup>1)</sup> Refered to as 'colbits'

<sup>2)</sup> Refered to as 'org'

3) PageSize = 2<sup>colbits</sup> × org/8 [Bytes]

**TABLE 9**

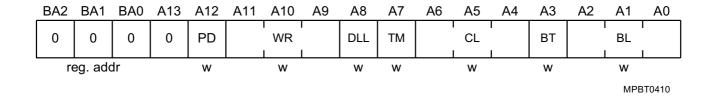

HYB18T256[40/80/16]0AF(L)–[2.5/25F/3/3S/3.7/5] 256-Mbit DDR2 SDRAM

Mode Register Definition (BA[2:0] = 000B)

# 3 Functional Description

| Field | Bits   | Type <sup>1)</sup> | Description                                                            |

|-------|--------|--------------------|------------------------------------------------------------------------|

| BA2   | 16     | reg. addr.         | Bank Address [2]                                                       |

|       |        |                    | Note: BA2 not available on 256 Mbit and 512 Mbit components            |

|       |        |                    | 0 <sub>B</sub> <b>BA2</b> Bank Address                                 |

| BA1   | 15     | 1                  | Bank Address [1]                                                       |

|       |        |                    | 0 <sub>B</sub> <b>BA1</b> Bank Address                                 |

| BA0   | 14     |                    | Bank Address [0]                                                       |

|       |        |                    | 0 <sub>B</sub> <b>BA0</b> Bank Address                                 |

| A13   | 13     |                    | Address Bus [13]                                                       |

|       |        |                    | Note: A13 is not available for 256 Mbit and x16 512 Mbit configuration |

|       |        |                    | 0 <sub>B</sub> A13 Address bit 13                                      |

| PD    | 12     | w                  | Active Power-Down Mode Select                                          |

|       |        |                    | 0 <sub>B</sub> <b>PD</b> Fast exit                                     |

|       |        |                    | 1 <sub>B</sub> <b>PD</b> Slow exit                                     |

| WR    | [11:9] | w                  | Write Recovery 2)                                                      |

Note: All other bit combinations are illegal.

$\begin{array}{ccc} 001_B & \text{WR } 2 \\ 010_B & \text{WR } 3 \\ 011_B & \text{WR } 4 \\ 100_B & \text{WR } 5 \\ 101_B & \text{WR } 6 \\ \end{array}$

**DLL Reset**

**Test Mode**

$0_{B}$

1<sub>B</sub>

$0_{B}$

**DLL** No

**DLL** Yes

TM Normal Mode

TM Vendor specific test mode

DLL

TM

8

W

| Field | Bits  | Type <sup>1)</sup> | Description                                                                                                                                                              |

|-------|-------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL    | [6:4] | w                  | CAS Latency Note: All other bit combinations are illegal.  011 <sub>B</sub> CL 3 100 <sub>B</sub> CL 4 101 <sub>B</sub> CL 5 110 <sub>B</sub> CL 6 111 <sub>B</sub> CL 7 |

| ВТ    | 3     | w                  | Burst Type 0 <sub>B</sub> BT Sequential 1 <sub>B</sub> BT Interleaved                                                                                                    |

| BL    | [2:0] | w                  | Burst Length Note: All other bit combinations are illegal.  010 <sub>B</sub> BL 4 011 <sub>B</sub> BL 8                                                                  |

<sup>1)</sup> w = write only register bits

Number of clock cycles for write recovery during auto-precharge. WR in clock cycles is calculated by dividing  $t_{\text{WR}}$  (in ns) by  $t_{\text{CK}}$  (in ns) and rounding up to the next integer: WR [cycles]  $\geq t_{\text{WR}}$  (ns)  $/ t_{\text{CK}}$  (ns). The mode register must be programmed to fulfill the minimum requirement for the analogue  $t_{\text{WR}}$  timing  $WR_{\text{MIN}}$  is determined by  $t_{\text{CK.MAX}}$  and  $WR_{\text{MAX}}$  is determined by  $t_{\text{CK.MIN}}$ .

| BA2       | BA1 | BA0 | A13 | A12              | A11  | A10 | A9 | A8     | A7       | A6              | A5 | A4 | A3 | A2       | A1  | A0    |

|-----------|-----|-----|-----|------------------|------|-----|----|--------|----------|-----------------|----|----|----|----------|-----|-------|

| 0         | 0   | 1   | 0   | Q <sub>off</sub> | RDQS | DQS | OC | D Prog | ram<br>I | R <sub>tt</sub> |    | AL |    | $R_{tt}$ | DIC | DLL   |

| reg. addr |     |     |     |                  | W    | W   |    | W      |          | W               |    | W  |    | W        | W   | W     |

|           |     |     |     |                  |      |     |    |        |          |                 |    |    |    |          | MPB | T0380 |

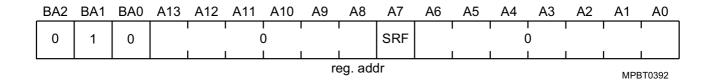

#### TABLE 10 Extended Mode Register Definition (BA[2:0] = 001B) **Field Bits** Type<sup>1)</sup> **Description** BA2 16 Bank Address [2] reg. addr. Note: BA2 not available on 256 Mbit and 512 Mbit components **BA2** Bank Address BA1 Bank Address [1] 15 **BA1** Bank Address Bank Address [0] BA0 14 **BA0** Bank Address A13 13 Address Bus [13] w Note: A13 is not available for 256 Mbit and x16 512 Mbit configuration A13 Address bit 13 **Output Disable** Qoff 12 **QOff** Output buffers enabled **QOff** Output buffers disabled Read Data Strobe Output (RDQS, RDQS) **RDQS** 11 **RDQS** Disable **RDQS** Enable DQS **Complement Data Strobe (DQS Output)** 10 **DQS** Enable $0_{B}$ **DQS** Disable OCD [9:7] **Off-Chip Driver Calibration Program** 000<sub>B</sub> OCD OCD calibration mode exit, maintain setting Program 001<sub>B</sub> **OCD** Drive (1) 010<sub>B</sub> **OCD** Drive (0) 100<sub>B</sub> **OCD** Adjust mode 111<sub>B</sub> OCD OCD calibration default

| Field           | Bits  | Type <sup>1)</sup> | Description                                                                                                                                                                                                             |

|-----------------|-------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AL              | [5:3] | _                  | Additive Latency  Note: All other bit combinations are illegal.                                                                                                                                                         |

|                 |       |                    | 000 <sub>B</sub> AL 0<br>001 <sub>B</sub> AL 1<br>010 <sub>B</sub> AL 2<br>011 <sub>B</sub> AL 3<br>100 <sub>B</sub> AL 4                                                                                               |

| R <sub>TT</sub> | 6,2   |                    | Nominal Termination Resistance of ODT  Note: See "ODT DC Electrical Characteristics" on Page 26  00 <sub>B</sub> RTT ∞ (ODT disabled) 01 <sub>B</sub> RTT 75 Ohm 10 <sub>B</sub> RTT 150 Ohm 11 <sub>B</sub> RTT 50 Ohm |

| DIC             | 1     |                    | Off-chip Driver Impedance Control  0 <sub>B</sub> DIC Full (Driver Size = 100%)  1 <sub>B</sub> DIC Reduced                                                                                                             |

| DLL             | 0     |                    | DLL Enable  0 <sub>B</sub> DLL Enable  1 <sub>B</sub> DLL Disable                                                                                                                                                       |

<sup>1)</sup> w = write only register bits

#### TABLE 11

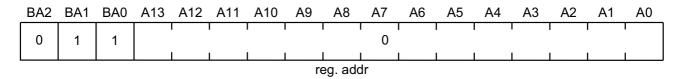

#### EMRS(2) Programming Extended Mode register Definition (BA[2:0]=010<sub>B</sub>) Field Bits Type<sup>1)</sup> **Description** BA2 16 Bank Address [2] reg.addr Note: BA2 is not available on 256Mbit and 512Mbit components **BA2** Bank Address BA1 15 Bank Adress [1] **BA1** Bank Address BA0 14 Bank Adress [0] **BA0** Bank Address Address Bus [13:8] Α [13:8] Note: A13 is not available for 256 Mbit and x16 512 Mbit configuration A [13:8] Address bits **SRF** [7] Address Bu s[7] W Note: When DRAM is operated at 85 °C $\leq$ $T_{CASE}$ < 95 °C the extended self refresh rate must be enabled by setting bit A7 to "1" before the self refresh mode can be entered. $0_{B}$ A7 disable A7 enable, adapted self refresh rate for $T_{\rm CASE}$ > 85 °C $1_{B}$ Address Bus [6:0] Α [6:0] w A [6:0] Address bits $0_{R}$

<sup>1)</sup> w = write only

MPBT0400

# TABLE 12

#### EMR(3) Programming Extended Mode Register Definition (BA[2:0]=010<sub>B</sub>)

|       | Emit(o) Frogramming Extended mode Register Definition (DA[E.0] 010B) |                    |                                                                                                                                  |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Field | Bits                                                                 | Type <sup>1)</sup> | Description                                                                                                                      |  |  |  |  |  |  |

| BA2   | 16                                                                   | reg.addr           | Bank Address [2]  Note: BA2 is not available on 256 Mbit and 512 Mbit components                                                 |  |  |  |  |  |  |

|       |                                                                      |                    | 0 <sub>B</sub> <b>BA2</b> Bank Address                                                                                           |  |  |  |  |  |  |

| BA1   | 15                                                                   |                    | Bank Adress [1] 1 <sub>B</sub> BA1 Bank Address                                                                                  |  |  |  |  |  |  |

| BA0   | 14                                                                   |                    | Bank Adress [0] 1 <sub>B</sub> BA0 Bank Address                                                                                  |  |  |  |  |  |  |

| A     | [13:0]                                                               | w                  | Address Bus [13:0]  Note: A13 is not available for 256 Mbit and x16 512 Mbit configuration  0 <sub>B</sub> A [13:0] Address bits |  |  |  |  |  |  |

<sup>1)</sup> w = write only

# **TABLE 13**

|                |                         | ODT Truth Table         |

|----------------|-------------------------|-------------------------|

| Input Pin      | EMRS(1) Address Bit A10 | EMRS(1) Address Bit A11 |

| ×4 components  |                         |                         |

| DQ[3:0]        | X                       |                         |

| DQS            | X                       |                         |

| DQS            | 0                       | X                       |

| DM             | X                       |                         |

| ×8 components  |                         |                         |

| DQ[7:0]        | X                       |                         |

| DQS            | X                       |                         |

| DQS            | 0                       | X                       |

| RDQS           | X                       | 1                       |

| RDQS           | 0                       | 1                       |

| DM             | X                       | 0                       |

| ×16 components |                         |                         |

| DQ[7:0]        | X                       |                         |

| DQ[15:8]       | X                       |                         |

| LDQS           | X                       |                         |

| LDQS           | 0                       | X                       |

| UDQS           | X                       |                         |

| UDQS           | 0                       | X                       |

| LDM            | X                       |                         |

| UDM            | X                       |                         |

Note: X = don't care; 0 = bit set to low; 1 = bit set to high

### **TABLE 14**

#### **Burst Length and Sequence**

|              |                                |                                 | Burst Length and Sequence       |

|--------------|--------------------------------|---------------------------------|---------------------------------|

| Burst Length | Starting Address<br>(A2 A1 A0) | Sequential Addressing (decimal) | Interleave Addressing (decimal) |

| 4            | × 0 0                          | 0, 1, 2, 3                      | 0, 1, 2, 3                      |

|              | × 0 1                          | 1, 2, 3, 0                      | 1, 0, 3, 2                      |

|              | ×1 0                           | 2, 3, 0, 1                      | 2, 3, 0, 1                      |

|              | ×1 1                           | 3, 0, 1, 2                      | 3, 2, 1, 0                      |

| 8            | 0 0 0                          | 0, 1, 2, 3, 4, 5, 6, 7          | 0, 1, 2, 3, 4, 5, 6, 7          |

|              | 0 0 1                          | 1, 2, 3, 0, 5, 6, 7, 4          | 1, 0, 3, 2, 5, 4, 7, 6          |

|              | 0 1 0                          | 2, 3, 0, 1, 6, 7, 4, 5          | 2, 3, 0, 1, 6, 7, 4, 5          |

|              | 0 1 1                          | 3, 0, 1, 2, 7, 4, 5, 6          | 3, 2, 1, 0, 7, 6, 5, 4          |

|              | 100                            | 4, 5, 6, 7, 0, 1, 2, 3          | 4, 5, 6, 7, 0, 1, 2, 3          |

|              | 1 0 1                          | 5, 6, 7, 4, 1, 2, 3, 0          | 5, 4, 7, 6, 1, 0, 3, 2          |

|              | 1 1 0                          | 6, 7, 4, 5, 2, 3, 0, 1          | 6, 7, 4, 5, 2, 3, 0, 1          |

|              | 1 1 1                          | 7, 4, 5, 6, 3, 0, 1, 2          | 7, 6, 5, 4, 3, 2, 1, 0          |

<sup>1.</sup> Page Size and Length is a function of I/O organization: Page size for all 256 Mbit components is 1 KByte

<sup>2.</sup> Order of burst access for sequential addressing is "nibble-based" and therefore different from SDR or DDR components

# 4 Truth Tables

This chapter describes the truth tables.

|                                 |                   |                  |    |     |     |    |     |          | Co  |        | ABLE 15 Truth Table    |

|---------------------------------|-------------------|------------------|----|-----|-----|----|-----|----------|-----|--------|------------------------|

| Function                        | CKE               |                  | CS | RAS | CAS | WE | BA0 | A[12:11] | A10 | A[9:0] | Note <sup>1)2)3)</sup> |

|                                 | Previous<br>Cycle | Current<br>Cycle |    |     |     |    | BA1 |          |     |        |                        |

| (Extended) Mode<br>Register Set | Н                 | Н                | L  | L   | L   | L  | ВА  | OP Code  | •   |        | 4)5)                   |

| Auto-Refresh                    | Н                 | Н                | L  | L   | L   | Н  | Х   | Х        | Х   | Х      | 4)                     |

| Self-Refresh Entry              | Н                 | L                | L  | L   | L   | Н  | Х   | Х        | Х   | Х      | 4)6)                   |

| Self-Refresh Exit               | L                 | Н                | Н  | Х   | Х   | Х  | Х   | Х        | Х   | Х      | 4)6)7)                 |

|                                 |                   |                  | L  | Н   | Н   | Н  |     |          |     |        |                        |

| Single Bank Precharge           | Н                 | Н                | L  | L   | Н   | L  | ВА  | Х        | L   | Х      | 4)5)                   |

| Precharge all Banks             | Н                 | Н                | L  | L   | Н   | L  | Х   | Х        | Н   | Х      | 4)                     |

| Bank Activate                   | Н                 | Н                | L  | L   | Н   | Н  | ВА  | Row Addr | ess |        | 4)5)                   |

| Write                           | Н                 | Н                | L  | Н   | L   | L  | ВА  | Column   | L   | Column | 4)5)8)                 |

| Write with Auto-<br>Precharge   | Н                 | Н                | L  | Н   | L   | L  | ВА  | Column   | Н   | Column | 4)5)8)                 |

| Read                            | Н                 | Н                | L  | Н   | L   | Н  | ВА  | Column   | L   | Column | 4)5)8)                 |

| Read with Auto-<br>Precharge    | Н                 | Н                | L  | Н   | L   | Н  | ВА  | Column   | Н   | Column | 4)5)8)                 |

| No Operation                    | Н                 | Х                | L  | Н   | Н   | Н  | Х   | Х        | Х   | Х      | 4)                     |

| Device Deselect                 | Н                 | Х                | Н  | Х   | Х   | Х  | Х   | Х        | Х   | Х      | 4)                     |

| Power Down Entry                | Н                 | L                | Н  | Х   | Х   | Х  | Х   | Х        | Х   | Х      | 4)9)                   |

|                                 |                   |                  | L  | Н   | Н   | Н  | 1   |          |     |        |                        |

| Power Down Exit                 | L                 | Н                | Н  | Х   | Х   | Х  | Х   | Х        | Х   | Х      | 4)9)                   |

|                                 |                   |                  | L  | Н   | Н   | Н  | 1   |          |     |        |                        |

- 1) The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh.

- 2) "X" means "H or L (but a defined logic level)".

- 3) Operation that is not specified is illegal and after such an event, in order to guarantee proper operation, the DRAM must be powered down and then restarted through the specified initialization sequence before normal operation can continue.

- 4) All DDR2 SDRAM commands are defined by states of CS, WE, RAS, CAS, and CKE at the rising edge of the clock.

- 5) Bank addresses BA[1:0] determine which bank is to be operated upon. For (E)MRS BA[1:0] selects an (Extended) Mode Register.

- 6)  $V_{\rm REF}$  must be maintained during Self Refresh operation.

- 7) Self Refresh Exit is asynchronous.

- 8) Burst reads or writes at BL = 4 cannot be terminated.

- 9) The Power Down Mode does not perform any refresh operations. The duration of Power Down is therefore limited by the refresh requirements.

#### **TABLE 16**

#### Clock Enable (CKE) Truth Table for Synchronous Transitions Current State<sup>1)</sup> **CKE** Command (N)<sup>2)3)</sup> Action (N)2) Note<sup>4)5)</sup> RAS, CAS, WE Previous Cycle<sup>6)</sup> Current Cycle<sup>6)</sup> (N-1)(N) 7)8)11) Power-Down L Maintain Power-Down 7)9)10)11) ı Н DESELECT or NOP Power-Down Fxit 8)11)12) Self Refresh L Maintain Self Refresh 9)12)13)14) Н DESELECT or NOP Self Refresh Exit 7)9)10)11)15) Bank(s) Active Н L DESELECT or NOP Active Power-Down Entry 9)10)11)15) All Banks Idle Н L DESELECT or NOP Precharge Power-Down Entry 7)11)14)16) Н **AUTOREFRESH** Self Refresh Entry Т 17) Н Н Refer to the Command Truth Table Any State other than listed above

- 1) Current state is the state of the DDR2 SDRAM immediately prior to clock edge N.

- 2) Command (N) is the command registered at clock edge N, and Action (N) is a result of Command (N).

- 3) The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh.

- 4) CKE must be maintained HIGH while the device is in OCD calibration mode.

- 5) Operation that is not specified is illegal and after such an event, in order to guarantee proper operation, the DRAM must be powered down and then restarted through the specified initialization sequence before normal operation can continue.

- 6) CKE (N) is the logic state of CKE at clock edge N; CKE (N-1) was the state of CKE at the previous clock edge.

- 7) The Power-Down Mode does not perform any refresh operations. The duration of Power-Down Mode is therefor limited by the refresh requirements.

- 8) "X" means "don't care (including floating around  $V_{\rm REF}$ )" in Self Refresh and Power Down. However ODT must be driven HIGH or LOW in Power Down if the ODT function is enabled (Bit A2 or A6 set to "1" in EMRS(1)).

- 9) All states and sequences not shown are illegal or reserved unless explicitly described elsewhere in this document.

- 10) Valid commands for Power-Down Entry and Exit are NOP and DESELECT only.

- 11)  $t_{\text{CKE.MIN}}$  of 3 clocks means CKE must be registered on three consecutive positive clock edges. CKE must remain at the valid input level the entire time it takes to achieve the 3 clocks of registration. Thus, after any CKE transition, CKE may not transition from its valid level during the time period of  $t_{\text{IS}} + 2xt_{\text{CKE}} + t_{\text{IH}}$ .

- 12)  $V_{\rm RFF}$  must be maintained during Self Refresh operation.

- 13) On Self Refresh Exit DESELECT or NOP commands must be issued on every clock edge occurring during the tXSNR period. Read commands may be issued only after t<sub>XSRD</sub> (200 clocks) is satisfied.

- 14) Valid commands for Self Refresh Exit are NOP and DESELCT only.

- 15) Power-Down and Self Refresh can not be entered while Read or Write operations, (Extended) mode Register operations, Precharge or Refresh operations are in progress.

- 16) Self Refresh mode can only be entered from the All Banks Idle state.

- 17) Must be a legal command as defined in the Command Truth Table.

# TABLE 17

|                 | Dat | a Mask (DM) | <b>Truth Table</b> |

|-----------------|-----|-------------|--------------------|

| Name (Function) | DM  | DQs         | Note               |

| Write Enable    | L   | Valid       | 1)                 |

| Write Inhibit   | Н   | Χ           | 1)                 |

<sup>1)</sup> Used to mask write data; provided coincident with the corresponding data.

# 5 AC & DC Operating Conditions

This chapter contains the DC operating conditions tables.

# 5.1 Absolute Maximum Ratings

This chapter contains the absolute minimum ratings table.

|                    |                                                       |              | TABLE 18 Absolute Maximum Ratings |

|--------------------|-------------------------------------------------------|--------------|-----------------------------------|

| Symbol             | Parameter                                             | Rating       | Unit Note                         |

| $V_{DD}$           | Voltage on $V_{\rm DD}$ pin relative to $V_{\rm SS}$  | -1.0 to +2.3 | V 1)2)                            |

| $V_{DDQ}$          | Voltage on $V_{\rm DDQ}$ pin relative to $V_{\rm SS}$ | -0.5 to +2.3 | V 1)2)                            |

| $V_{DDL}$          | Voltage on VDDL pin relative to $V_{\rm SS}$          | -0.5 to +2.3 | V 1)2)                            |

| $V_{IN},V_{OUT}$   | Voltage on any pin relative to $V_{\mathrm{SS}}$      | -0.5 to +2.3 | V 1)                              |

| $T_{\mathtt{STG}}$ | Storage Temperature                                   | -55 to +100  | °C 1)3)                           |

<sup>1)</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2) When  $V_{\rm DD}$  and  $V_{\rm DDQ}$  and  $V_{\rm DDL}$  are less than 500 mV;  $V_{\rm REF}$  may be equal to or less than 300 mV.

- 3) Storage Temperature is the case surface temperature on the center/top side of the DRAM.

|            |                       |                              | TAB      | LE 19    |

|------------|-----------------------|------------------------------|----------|----------|

|            |                       | DRAM Component Operating Ter | mperatur | e Range  |

| Symbol     | Parameter             | Rating                       | Unit     | Note     |

| $T_{OPER}$ | Operating Temperature | 0 to 95                      | °C       | 1)2)3)4) |

<sup>1)</sup> Operating Temperature is the case surface temperature on the center / top side of the DRAM.

<sup>2)</sup> The operating temperature range are the temperatures where all DRAM specification will be supported. During operation, the DRAM case temperature must be maintained between 0 - 95 °C under all other specification parameters.

<sup>3)</sup> Above 85 °C case temperature the Auto-Refresh command interval has to be reduced to  $t_{\rm REFI}$  = 3.9  $\mu s$ .

<sup>4)</sup> When operating this product in the 85 °C to 95 °C  $T_{\text{CASE}}$  temperature range, the High temperature Self Refresh has to be enabled by setting EMR(2) bit A7 to "1". Note, when the high Temperature Self Refresh is enabled there is an increase of  $I_{\text{DD6}}$  by approximately 50 %.

## 5.2 DC Characteristics

This chapter describes the DC characteristics.

|            |                           | R                     | ecommended           | DC Operating Co                |      | BLE 20<br>(SSTL 18) |

|------------|---------------------------|-----------------------|----------------------|--------------------------------|------|---------------------|

| Symbol     | Parameter                 | Rating                |                      |                                | Unit | Note                |

|            |                           | Min.                  | Тур.                 | Max.                           |      |                     |